Плата разработки Waveshare EP2C5 EP2C5T144C8N ALTERA Cyclone II FPGA = стандартная Бесплатная доставка |

Сохраните в закладки:

История цены

*История изменения цены! Указанная стоимость возможно, уже изменилось. Проверить текущую цену - >

| Месяц | Минимальная цена | Макс. стоимость | Цена |

|---|---|---|---|

| Sep-17-2025 | 0.40 руб. | 0.86 руб. | 0 руб. |

| Aug-17-2025 | 0.80 руб. | 0.68 руб. | 0 руб. |

| Jul-17-2025 | 0.90 руб. | 0.89 руб. | 0 руб. |

| Jun-17-2025 | 0.70 руб. | 0.54 руб. | 0 руб. |

| May-17-2025 | 0.17 руб. | 0.37 руб. | 0 руб. |

| Apr-17-2025 | 0.7 руб. | 0.17 руб. | 0 руб. |

| Mar-17-2025 | 0.17 руб. | 0.33 руб. | 0 руб. |

| Feb-17-2025 | 0.50 руб. | 0.23 руб. | 0 руб. |

| Jan-17-2025 | 0.82 руб. | 0.21 руб. | 0 руб. |

Новые товары

Raspberry Pi 3 Model B Plus специальный алюминиевый чехол с двойным охлаждающим

Модуль Yahboom AS608 объединяет оптический путь и функции обработки отпечатков пальцев для Raspberry Pi Micro:bit Jetson Nano.

Металлический корпус (А) с вентилятором для платы расширения Raspberry Pi Compute Module 4.

Оригинальный ST-Link V2 Stlink St Link STM32 STM8 MCU USB JTAG In-circuit Debugger/Programmer/Emulator.

Ядро STM32F405 для разработки платы IoT PyBoard на.

HY32D 3.2 дюйма 320 * 240 ЖК-сенсорный экран Дисплей XPT2046 Контроллер сенсорного экрана ILI9325 TFT модуль.

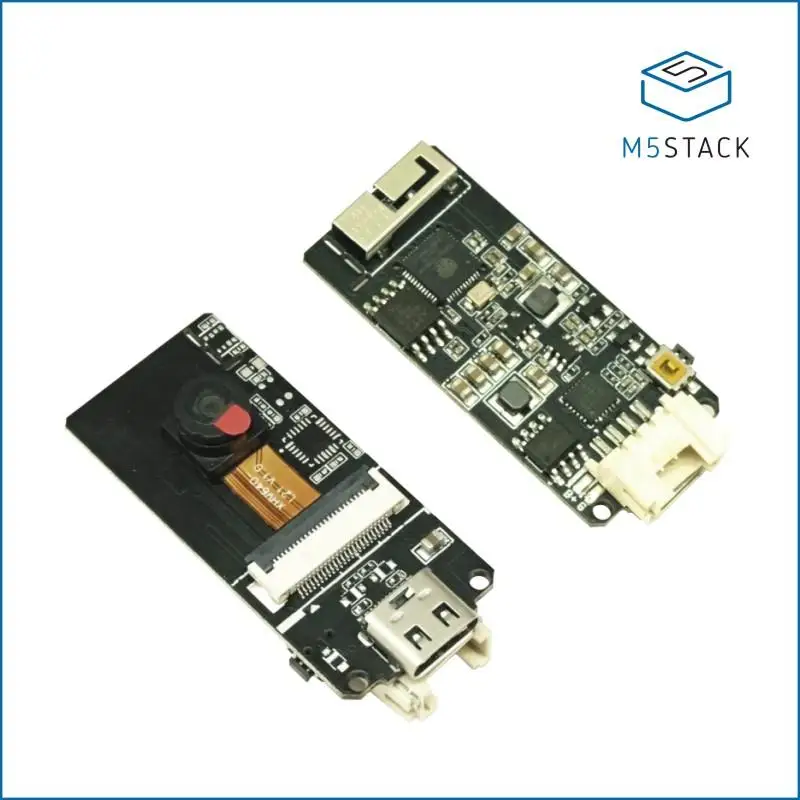

Официальная макетная плата модуля камеры M5Stack ESP32 (OV2640) | Демонстрационные стенды

Русский: Многофункциональный сигнальный генератор высокой стабильности с двумя каналами Feeltech FY2300 12M 20M Digital DDS Function Frequency Meter.

Характеристики

Плата разработки Waveshare EP2C5 EP2C5T144C8N ALTERA Cyclone II FPGA = стандартная Бесплатная доставка |

Описание товара

Обзор

Обзор

OpenEP3C5-C Это Плата развития FPGA, которая состоит из материнской платы DVK601 И основная плата FPGA CoreEP3C5.

OpenEP3C5-C поддерживает дальнейшее расширение с помощью различных дополнительных аксессуаров для конкретных приложений. Модульная и открытая конструкция делает его идеальным для запуска разработки приложений с устройствами ALTERA Cyclone III series FPGA. OpenEP3C5-C позволяет легко и быстро начать дизайн с процессором Nios II.

Что на материнском доске

FPGA CPLD разъем основной платы: Для легкого подключения основных плат, которые интегрируют чип FPGA CPLD на борту

Интерфейс 8I/Os_1, Для подключения комплектующих досок/модулей

Интерфейс 8I/Os_2, Для подключения комплектующих досок/модулей

Интерфейс 8I/Os_3, Для подключения комплектующих досок/модулей

Интерфейс 8I/Os_4, Для подключения комплектующих досок/модулей

Интерфейс 16I/Os_1, Для подключения комплектующих досок/модулей

Интерфейс 16I/Os_2, Для подключения комплектующих досок/модулей

Интерфейс 32I/Os_1, Для подключения комплектующих досок/модулей

Интерфейс 32I/Os_2, Для подключения комплектующих досок/модулей

FPGA CPLD разъем основной платы: Для легкого подключения основных плат, которые интегрируют чип FPGA CPLD на борту

Интерфейс 8I/Os_1, Для подключения комплектующих досок/модулей

Интерфейс 8I/Os_2, Для подключения комплектующих досок/модулей

Интерфейс 8I/Os_3, Для подключения комплектующих досок/модулей

Интерфейс 8I/Os_4, Для подключения комплектующих досок/модулей

Интерфейс 16I/Os_1, Для подключения комплектующих досок/модулей

Интерфейс 16I/Os_2, Для подключения комплектующих досок/модулей

Интерфейс 32I/Os_1, Для подключения комплектующих досок/модулей

Интерфейс 32I/Os_2, Для подключения комплектующих досок/модулей

Все интерфейсы ввода/вывода выше:

Способен моделироваться как USART, I2C, SPI, PS/2 и т. Д. Способен управлять устройствами, такими как FRAM, FLASH, USB, Ethernet и т. д. FPGA для расширения разъемов Контакты FPGA доступны на разъемах расширения Для подключения платы аксессуаров SDRAM ЖК-дисплей интерфейс, Для подключения LCD22, LCD12864, LCD1602 Однопроводный интерфейс: Легко подключается к однопроводным устройствам (К-92 посылка), таким как датчик температуры (DS18B20), электронный регистрационный номер (DS2401) и т. Д. Зуммер Джойстик: Пять положений Потенциометр: Для регулировки подсветки LCD22 или LCD12864, LCD1602 регулировка контрастности Зуммер джемпер Джойстик джемпер Одно-провода соединительныеДля джемперов 16-18:

Короткая перемычка для подключения к I/Os, используемая в коде примера Откройте перемычку для подключения к другим пользовательским контактам через перемычкиDVK601 поддерживает широкий спектр различных основных плат, поэтому некоторые интерфейсы могут быть не подключены и бесполезны при подключении к определенной основной плате.

Что на CoreEP3C5 EP3C5E144C8N: Устройство ALTERA Cyclone III FPGA с функциями:

Рабочая частота: 50 МГц

Операционной Напряжение: 1,15 в ~ 3,465 в

Посылка: QFP144

Ввода/вывода: 82

LEs: 5K

Оперативная память: 414kb

PLLs: 2

Отладки/программирования: Поддержка jtag

AMS1117-3.3, 3,3 V регулятор напряжения

AMS1117-2.5, 2,5 V регулятор напряжения

AMS1117-1.2, 1,2 V регулятор напряжения

EPCS16, Встроенная последовательная флэш-память, для хранения кода

Мощность индикатор

Светодиоды

Кнопка сброса

Nconfig кнопки: Для повторной настройки чипа FPGA, эквивалент перезарядки питания

Мощность переключатель

50 м активный кристаллический осциллятор

5V DC jack

JTAG интерфейс: Для отладки/программирования

FPGA булавки расширитель, VCC, GND и все порты ввода/вывода доступны на разъемах расширения для дальнейшего расширения

Светодиодный Джемперы, Короткие перемычки, чтобы управлять светодиодами

EP3C5E144C8N: Устройство ALTERA Cyclone III FPGA с функциями:

Рабочая частота: 50 МГц

Операционной Напряжение: 1,15 в ~ 3,465 в

Посылка: QFP144

Ввода/вывода: 82

LEs: 5K

Оперативная память: 414kb

PLLs: 2

Отладки/программирования: Поддержка jtag

AMS1117-3.3, 3,3 V регулятор напряжения

AMS1117-2.5, 2,5 V регулятор напряжения

AMS1117-1.2, 1,2 V регулятор напряжения

EPCS16, Встроенная последовательная флэш-память, для хранения кода

Мощность индикатор

Светодиоды

Кнопка сброса

Nconfig кнопки: Для повторной настройки чипа FPGA, эквивалент перезарядки питания

Мощность переключатель

50 м активный кристаллический осциллятор

5V DC jack

JTAG интерфейс: Для отладки/программирования

FPGA булавки расширитель, VCC, GND и все порты ввода/вывода доступны на разъемах расширения для дальнейшего расширения

Светодиодный Джемперы, Короткие перемычки, чтобы управлять светодиодами

Фото

OpenEP3C5-C макетная плата

OpenEP3C5-C макетная плата

OpenEP3C5-C панель для разработки

Материнская плата печатная плата для DVK601

FPGA основной плате CoreEP3C5

FPGA основной плате CoreEP3C5

Подключение к различные периферийные устройства

Подключение к 3,2 дюймов сенсорный экран ЖК-дисплей

Подключение к LCD12864

Подключение к LCD1602

Подключение к RS232 доска

Подключение к RS485 доска

Подключение к USB UART Board

Подключение к 8 SEG светодиодный плате

Подключение к 8 кнопкам

Подключение к 5 клавиатуре IO

Подключение к 4x4 клавиатуре

Подключение к плата EEPROM

Несколько периферийных устройств, подключенных к одному интерфейсу

Подключение к DataFlash доска

Подключение к сети Ethernet

Подключение к USB плате CY7C68013A

Подключение к NRF24L01 RF плате

Подключение к плате для хранения Micro SD

Подключение к плате VGA PS2

Подключение к SDRAM доска

Подключение к SDRAM доска

Подключение к любой вспомогательной плате, которая вам нужна

Примечание: OpenEP3C5-C не интегрирует любые функции программирования/отладки, требуется программист/отладчик.

Примеры

OpenEP3C5-C FPGA development board поставляется с различными примерами кодов для поддерживаемых периферийных устройств, которые позволяют быстро начать разработку собственного приложения.

Периферийное устройство Описание продукта: Интерфейс Verilog VHDL NIOS II C S29GL128P NorFLASH 32I/Os Y AT24CXX EEPROM I2C √ √ √ FM24CXX Фрам I2C √ √ √ AT45DBXX DATAFLASH SPI √ SD карта Флэш-память SPI √ H57V1262GTR SDRAM (синхронное динамическое ОЗУ) Параллельный √ PCF8563 РТК I2C √ DS18B20 Температура датчик 1-проводной √ √ √ SP3232 Последовательной связи UART √ √ √ SP3485 Последовательной связи UART √ √ √ PL2303 USB UART UART √ √ √ FT245 Usb-fifo Параллельный √ CY7C68013A USB устройство Ввода/вывода √ ENC28J60 Ethernet controller SPI √ Зуммер Звуковое устройство 1I/O (ШИМ) √ √ √ PS/2 клавиатуры Вход устройства PS/2 √ √ Одной кнопки Вход устройства ---- √ √ √ 4x4 клавиатуры Вход устройства 8I/Os √ √ √ Джойстик Вход устройства 5I/Os √ √ √ Светодиодный Дисплей устройства ---- √ √ √ 8 SEG светодиодный Дисплей устройства 13I/Os √ √ √ Монитор с видеографической матрицей Дисплей устройства VGA √ √ Персонаж ЖК-дисплей Дисплей устройства 11I/Os √ √ Графический ЖК-дисплей Дисплей устройства 11I/Os √ 3,2 дюймовый Мульти-Цвет ЖК-дисплей + сенсорный экран Устройство отображения + устройство ввода 32I/Os √Отладки/программирования Интерфейс

Плата разработки OpenEP3C5-C FPGA интегрирует интерфейс JTAG для программирования/отладки.

JTAG названия и описание сигнала Pin-код Название сигнала Описание продукта: 1 TCK Часы сигнала 2 GND Заземления сигнала 3 TDO Данных от устройства 4 VCC (многоцел) Цель источника питания 5 TMS Джтаг государственного управления машиной 6 NC Без подключения 7 NC Без подключения 8 NC Без подключения 9 TDI Данные устройства 10 GND Заземления сигнала Джтаг заголовок

Развития ресурсы

Руководство пользователя CD включает следующие ресурсы разработки:

Сопутствующее программное обеспечение (Quaters II, NIOS II и т. Д.) Демонстрационный код (Verilog, VHDL и NIOS II C) Схема (PDF) FPGA разработка документов (спецификации и т. Д.)Посылка содержит OpenEP3C5-C макетная плата x 1 4-контактный провод х 2 2-контактный провод x 2 Кабель питания USB x 1 Руководство пользователя CD x 1 -1 шт.

2

2

3

3

4

4

5

5

Трекер стоимости

Отзывы покупателей

Новые отзывы о товарах

Минималистический дизайн наряду с удобностью часов дают отличное сочетание, купил недавно, однако чёрный вариант советую больше белого. Ремень часов при... Читать отзыв полностью...

Купила детский вязанный свитер для своей малышки. Свитер яркий и несмотря на то, что осенний, теплый, приятный на ощупь,... Читать отзыв полностью...

Платье заказывала для себя в двух экземплярах-сирене вое и желтое. Доставили оперативно. Подошло идеально, размер соответствует. Материал очень приятный на... Читать отзыв полностью...

Решила обновить свои наволочки для подушек. Мне понравились именно эти с рождественскими рисунками персикового цвета, что смотрятся прикольно и... Читать отзыв полностью...

Классный детский боди. Сделан из качественного материала. Ткань плотная. Качественная строчка и ровная, нет торчащих ниток. Носим больше полугода,... Читать отзыв полностью...

Заказывали тут, для фотосессии с новорожденной дочей. Удобно одевать, максимально простое, и в то же время очень красивое! Юбочка нам... Читать отзыв полностью...

За такие деньги данный бюстгалтер это просто чудо. Искала бюстгалтер очень долгое время не могла найти подходящий, но этот оказался... Читать отзыв полностью...